# ENEL 453: Final Design Project Discrete ADC Group 2

Evan Barker

UCID: 30146985

**Kyle James**

UCID: 30160266

**Tavish Gunnoo**

UCID: 30175194

# **Table of Contents**

| Introduction                   |

|--------------------------------|

| Architecture                   |

| RTL Schematic                  |

| Pictures of Basys36            |

| Schematic Diagram of           |

| Circuit                        |

| Description of Main            |

| blocks8                        |

| Detailed Design                |

| Menu FSM                       |

| PWM ADC                        |

| R2R Ladder ADC17               |

| Successive Approximation FSM20 |

| External                       |

| circuit26                      |

| Al tool                        |

| use28                          |

| Implementation                 |

| Results29                      |

| Testing30                      |

| Conclusion31                   |

| Appendix 1: Code and XDC 32    |

| Appendix 2: Al                 |

| Transcripts94                  |

#### Introduction

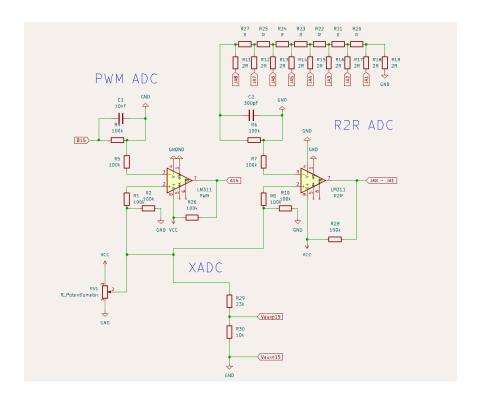

The goal of this design project was to implement several different types of digital-to-analog converters using SystemVerilog and an FPGA. Specifically, this included using the built-in XADC module in Vavido, as well as custom built ADCs using both a PWM and an R2R ladder in combination with external comparators. In addition to the ADC implementation, each subsystem was also designed to be able to display both hexadecimal and decimal values to the seven segment display onboard the FPGA. As an alternative to the ramp ADC, an additional successive approximation algorithm was introduced as an alternative method of fetching the digitized voltage value from the comparator. Overall, this project claims:

- This project report claims the 110% option:

- Sawtooth PWM and R2R ladder ADCs (70%)

- SAR PWM and R2R ladder ADCs (90%)

- Creative design (20%):

- 5% for 200 MHz clock from Clocking Wizard

- 5% for menu FSM (not just a mux)

- 10% for perfboard

Besides meeting the above requirements, our project also demonstrates "additional design requirements" which include following "synchronous design principles," "code formatting," etc.

Please use the following selects guide to understand which selects correspond to particular modes (gray code encoding):

0000 -> regular switches (last twelve on the BASYS board - everything to the left of R3) 0001 -> all zeros

#### 0011 -> XADC RAW

- 0010 -> XADC (averaged, but not scaled)

- 0110 -> XADC (averaged, and scaled)

#### 0111 -> PWM RAW

- 0101 -> PWM (averaged, but not scaled)

- 0100 -> PWM (averaged, and scaled)

#### 1100 -> R2R RAW

- 1101 -> R2R (averaged, but not scaled)

- 1111 -> R2R (averaged, and scaled)

#### 1000 -> PWM Successive RAW

- 1110 -> PWM Successive (averaged, but not scaled)

- 1010 -> PWM Successive (averaged, and scaled)

#### 1001 -> R2R Successive RAW

- 1011 -> R2R Successive (averaged, but not scaled)

- 1011 + down button (U17) (averaged, and scaled)

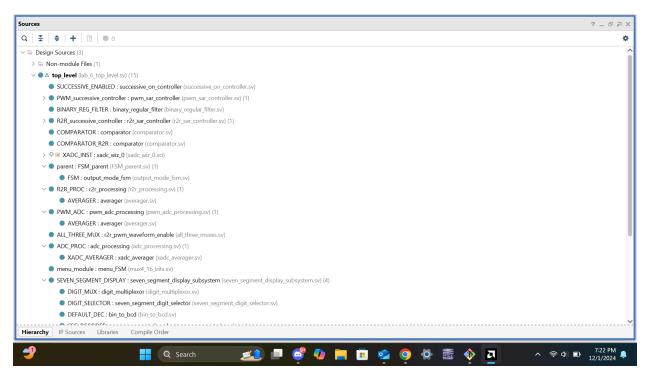

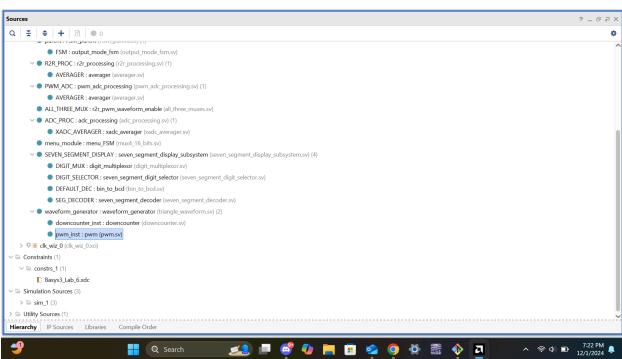

# **Architecture**

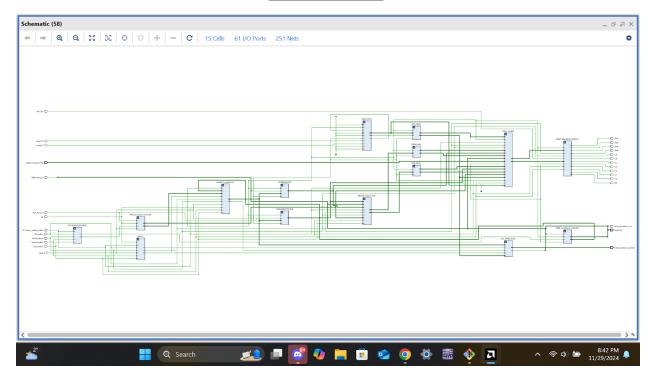

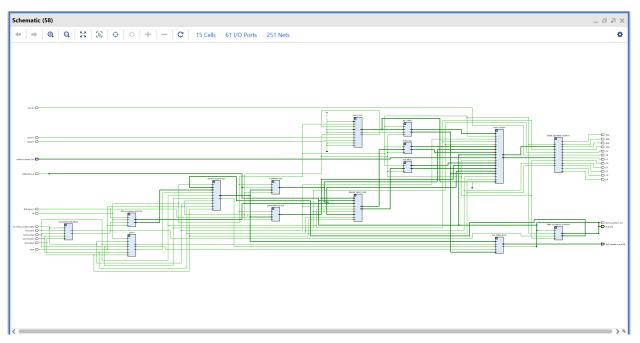

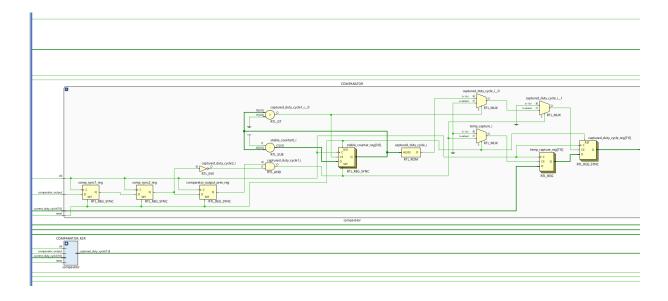

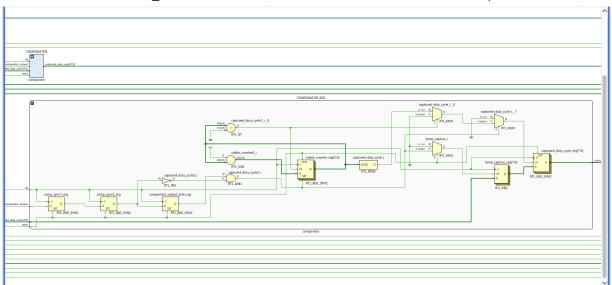

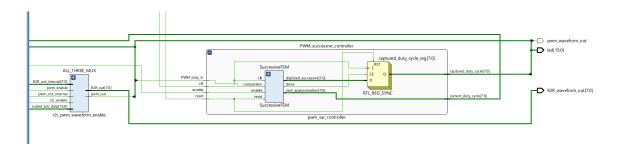

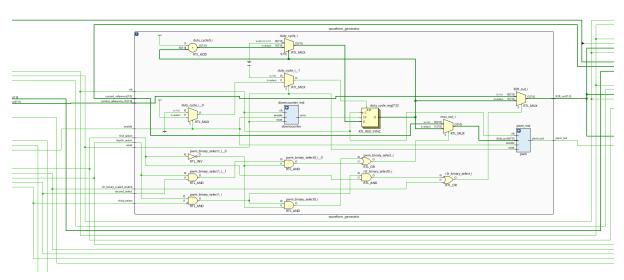

## **RTL Schematic**

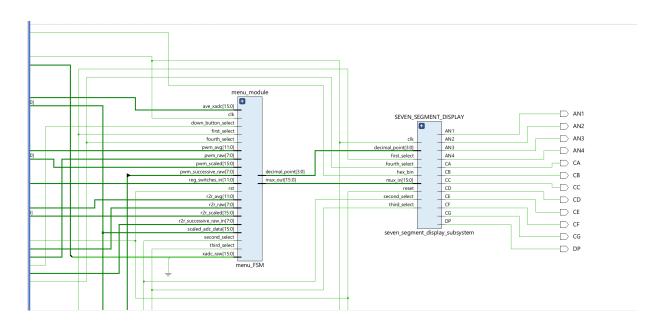

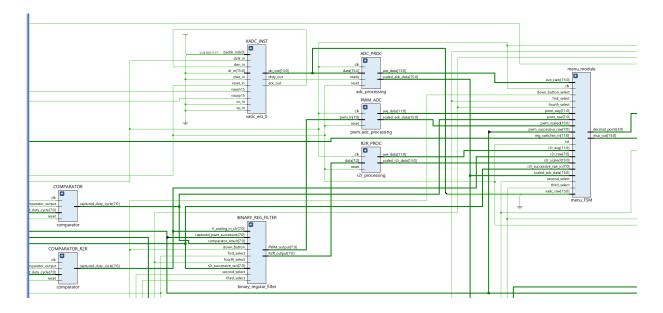

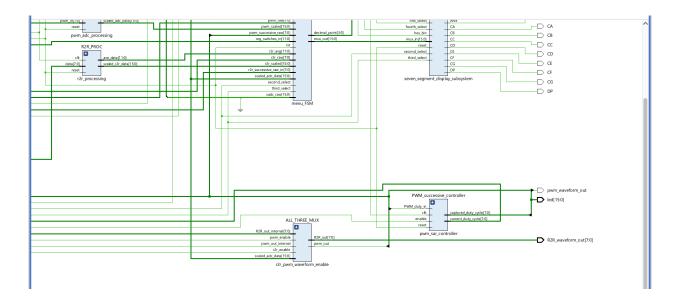

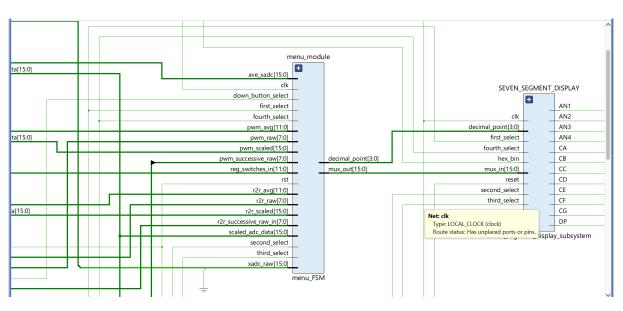

Overall RTL Schematic

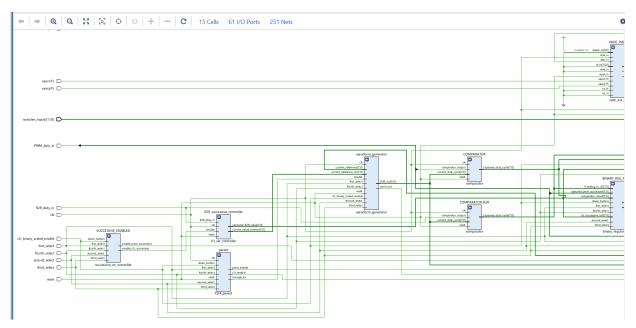

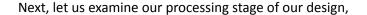

#### Zoomed-in left portion of RTL Schematic

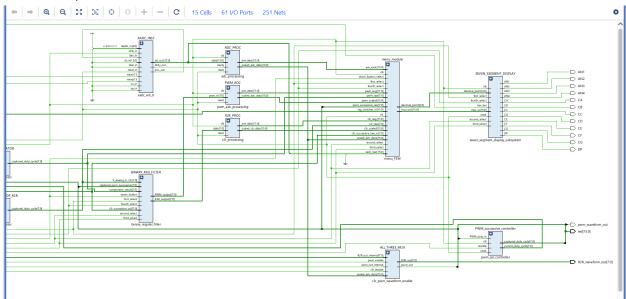

Zoomed-in right portion of RTL Schematic

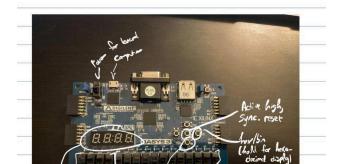

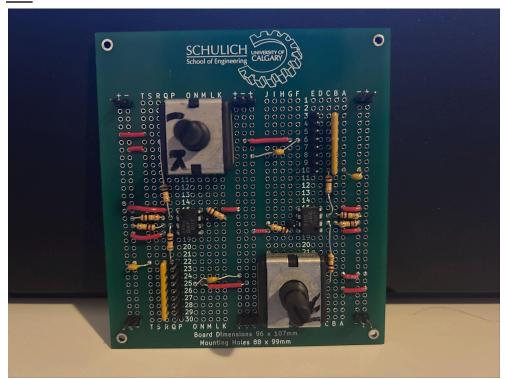

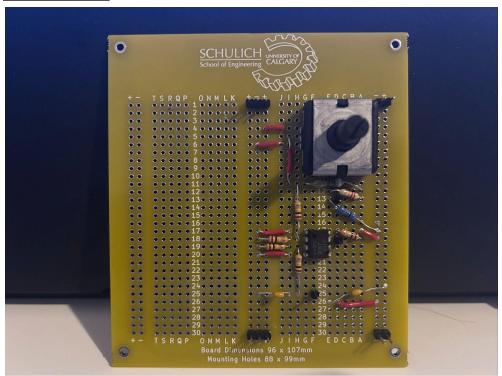

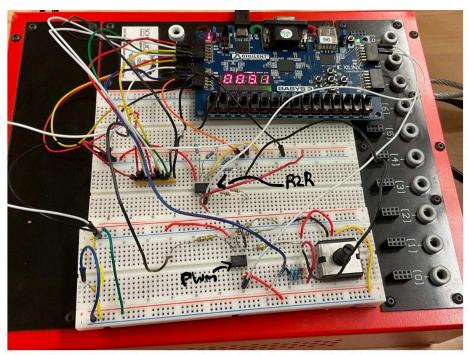

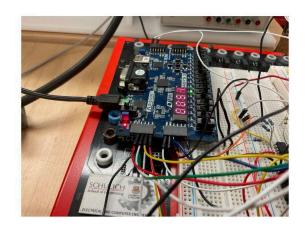

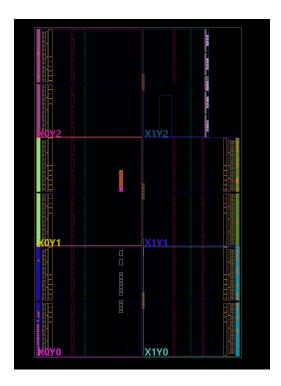

## **Pictures of Basys3**

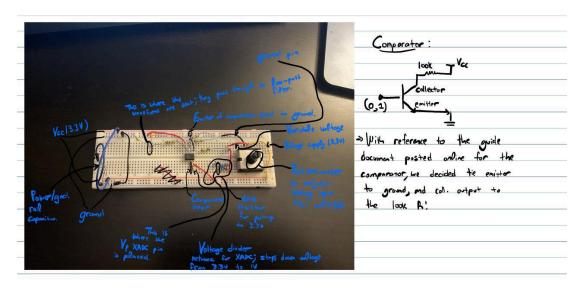

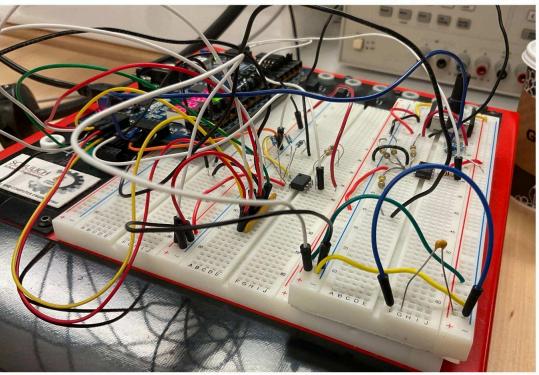

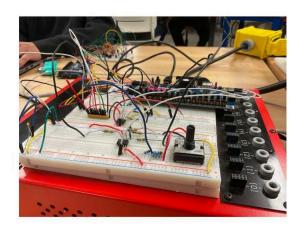

Above is the external circuitry. Annotations are provided for further understanding. As an additional note, for the purposes of testing we used a single comparator and swapped out the R2R ladder and PWM to the labeled nodes as needed. On demo day we will construct an external circuit with both comparators, allowing us to have entirely separate circuits for both the PWM and R2R ladder implementations. Please see the 'external circuitry' section for what the above looks like integrated as a broader circuit configuration.

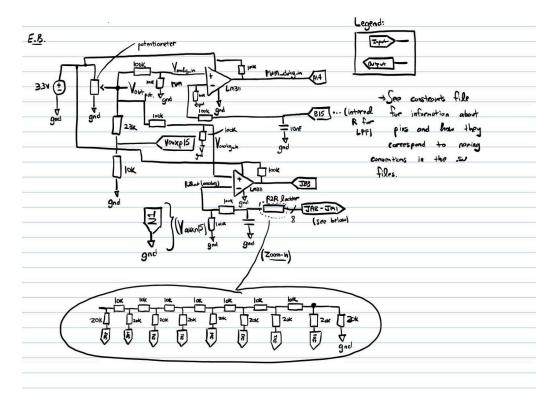

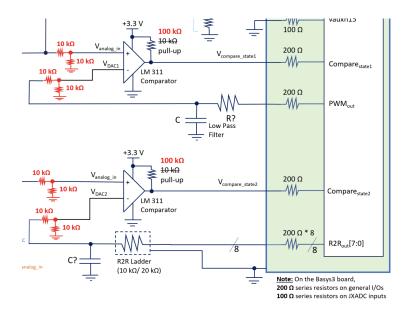

## **Schematic Diagram of Circuit**

## **Description of Main Blocks**

Let us start at the end of the architecture diagram, and work our way towards the beginning. We observe the following piece of architecture below,

The module named 'menu\_module' is our FSM which outputs the correct output depending on the provided select inputs. This output is fed into the seven segment display module via the 'mux\_out' bus to be displayed on the basys board. Additionally, a decimal point is conditionally displayed depending again on the selects provided as inputs to the 'SEVEN SEGMENT DISPLAY'.

Taking the comparator modules as inputs, the BINARY\_REG\_FILTER's purpose is to output either the regular or successive approximation outputs for the PWM and R2R implementations. For instance, for a select encoded as 0111, our BINARY\_REG\_FILTER will send the normal version of the PWM and R2R signals. However, if we chose to have 1000 for the selects, then BINARY\_REG\_FILTER will output the successive approximation signal for PWM and R2R. The purpose of the BINARY\_REG\_FILTER module is to 1) keep things more organized and condensed (less output wires compared to input wires) and 2) allow us to reuse PWM\_ADC and R2R\_PROC modules such that we don't need to add two additional modules for successive approximation method.

PWM\_ADC and R2R\_PROC both serve to process the raw values; embedded inside each are averager modules which find the average of the raw values. We chose to extend the raw signal by 4-bits (averaged output is 12 bits) because 1) that is what was done with XADC and 2) it seemed like the right 'sweet spot' between resource usage and largest number of resolution bits. In other words, at a certain point we will begin to experience diminishing returns in terms of WNS due to the additional hardware required by the increase in resolution bits. In addition to the averager module, the processing modules also contain scaling functionality that allow us to interpret voltage from 0.00V to 3.30V. We essentially used the scalings from 'ADC\_PROC' module but tweaked the shift and multiplication values to work with our voltage divided input; that is, we got,

```

module pwm_adc_processing #(

parameter int SCALING_FACTOR = 3400,

parameter int SHIFT_FACTOR = 8,

parameter int INPUT_BITS = 8,

parameter int AVERAGE_POWER = 8

) (

// Scale normalized value to voltage range

scaled_temp <= normalized_value * SCALING_FACTOR;

if ((scaled_temp >> SHIFT_FACTOR) > 16'd3300) begin

scaled_adc_data <= 16'd3300;

end else begin

scaled_adc_data <= scaled_temp >> SHIFT_FACTOR;

end

conversion_done <= 1'bl;

```

Finally, the top two modules are part of the XADC subsystem. The first module, XADC\_INST, is our IP generated module that converts the internal analog to digital signal. The second module, ADC\_PROC, finds the average and scaled values of the raw converted digital value coming out of XADC\_INST.

Looking at the leftmost part of our design, we observe both the comparator modules on the right side. The point of these is to capture the falling edge of the PWM\_duty\_in and R2R\_duty\_in inputs (outputs from comparator) such that it can take a snapshot of R2R\_out[7:0] at that point in time. That R2R\_out[7:0] digital value will represent the digital value corresponding to the analog input test voltage. Next, the waveform\_generator functions literally as its name describes; it generates a PWM\_waveform (ramp), and will allow for the 'counting up' for R2R\_out so that the comparators can take a 'snapshot' of a particular R2R\_out value. Inside of it (more later in detail section), we have embedded controls for successive so that the 'pwm\_out' output can resemble a duty cycle/pulse rather than ramp). Now, for the R2R\_successive\_controller. The point of this module, alongside PWM\_successive\_conroller (see

below), is to allow for the 'current\_duty\_cycle' (i.e., 1000\_0000, 0100\_0000, etc. intermediate digital reference voltages) value to pass through the waveform\_generator module to become an analog voltage such that it can be compared with analog input test voltage *again*. Also, the 'meat' of how the successive FSM functions is all embedded and abstracted within the R2R\_successive\_controller and

PWM\_successive\_controller modules (more on this later). Finally, for the two modules on the very left, these are quite simple; the 'parent' module just enables pwm or r2r, and enables the downcounter and duty cycle inside of waveform\_generator depending on the logic of the selects. The SUCCESSIVE\_ENABLED module enables the R2R successive or PWM successive depending on the logic of the selects that are inputs.

Finally, we have ALL\_THREE\_MUX which just will either 'zero' the pwm\_out or R2R\_out values or allow them to pass through from waveform\_generator depending on the logic of the selects. Finally, we see our PWM\_successive\_controller here also (already talked about this, scroll up).

# **Detailed Design**

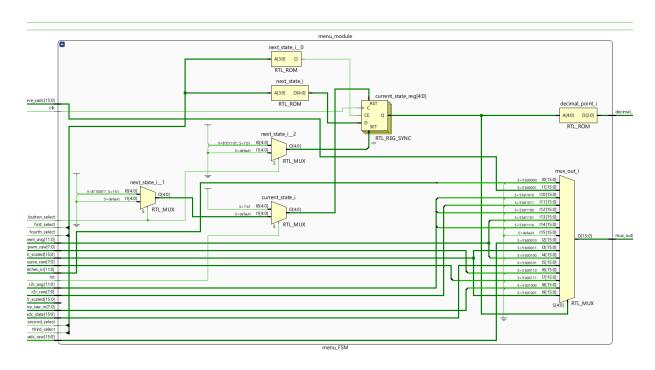

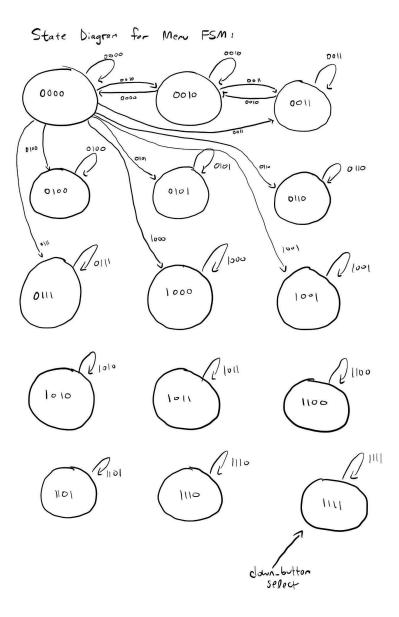

## **Menu FSM**

NOTE: For the state diagram above, not all of the connections above are shown; this is because there are too many involved - beyond a certain number of connections, the graph would no longer be helpful in illustrating states/ changes of the states. But, to summarize, the logic of the state machine is:

- IF (select\_input) is the same (select\_input) for previous clock cycle;

- THEN: maintain the same state.

- ELSE IF (select\_input) is not the same (select\_input) for previous clock cycle;

- THEN: change the state according to the new select\_input going into the next clock cycle.

Overall, compared to solely using regular muxes, the FSM allows for synchronization which will provide more stable values and will lead to more stable operation in the system overall. Note also that the reset

isn't displayed for the state machine as it is handled in the seven segment module in a combinational fashion. We observe a full mux in the second figure above in order to help 'filter' or 'choose' the particular inputs that will be used going into the next CLK cycle. We also have a ROM for the decimal point - so, depending on the select, a decimal will be added to the seven segment (i.e., if we choose 0110 (XADC averaged AND scaled) over 0111, we will get a decimal place displayed on the seven segment).

#### **PWM ADC**

As described in our external circuit schematic, the PWM signal is taken from the J3 output pin of our FPGA. The PWM signal generation can be found in "waveform\_generator", which sends a pulse train of increasing duty cycle to the low pass filter, which in terms smooths the signal and provides our comparator with a sawtooth wave. In combination with the variable input voltage to the positive input to the comparator, we are able to receive information about our analog input voltage via the duty cycle of our comparator output. Specifically, when our analog input is higher than the current value of our sawtooth wave, the comparator output will be floating, and subsequently pulled up by our pull-up configuration. When our sawtooth wave surpasses the analog input voltage, our comparator output will be grounded.

Given our analog input voltage is now captured in the duty cycle of our comparator output, we must extract this information using an additional module. This is done by providing the R2R output signal - which is the current 8-bit pwm value - as inputs to our COMPARATOR module. This way, upon detecting a logic zero from the the output of the comparator chip, our module can immediately store the current duty cycle and update the output value upon the next clock cycle. After the capturing phase, this signal is processed for averaging and scaling, or directly displayed depending on our current select and the logic encapsulated by our menu FSM module.

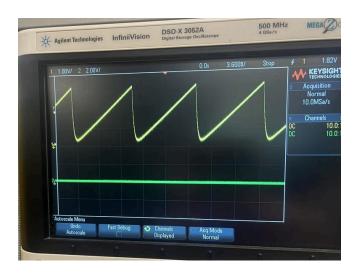

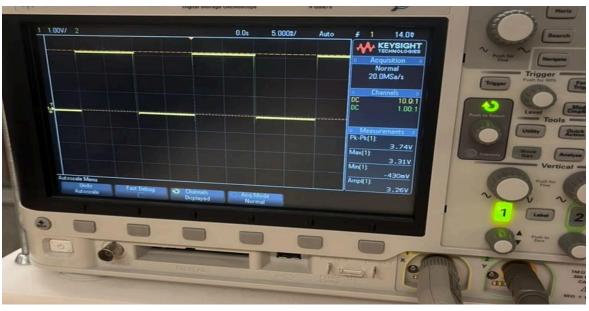

Figure above depicts what the PWM ramp should look like; note that it was crucial to choose the optimal capacitor value and R value for low pass filter such that a clean looking ramp is outputted.

Graph above depicts the duty cycle output from the comparator; this shows when the input test voltage is lower since we have a drop from 1 to 0 sooner within the given time frame of a period.

Graph above depicts the duty cycle output from the comparator; this shows when the input test voltage is higher since we have a drop from 1 to 0 later within the given time frame of a period. Note also that there is some marginal noise for the steady voltage 'HIGH' and voltage 'LOW' values; to assuage this, we can add small decoupling capacitors (1nF or less) to eliminate the extra static noise.

Inside the comparator module for PWM ADC, this is what things looked like,

Looking at the code above in combination with our circuitry, we see the falling edge detection logic that allow for the the capturing of the comparator duty cycle. That is, if our comparator\_output\_prev (previous comparator output) is a logic high, and comp\_sync2 is logic low, then our temp\_capture is updated with the current\_duty\_cycle. Note that additional checks where added for noise filtering to help with stability. This is implemented by setting stable\_counter to 0xFFFF, and ensuring our output signal has stabilized to zero for the period of time to takes for stable\_counter to reach a value of 1, where only then is our captured\_duty\_cycle updated to our new detected value. This ensures that our seven segment display is only updated when a stable reading has been obtained.

#### **R2R Ladder ADC**

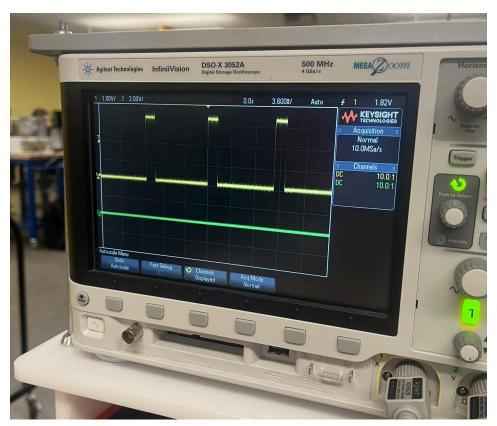

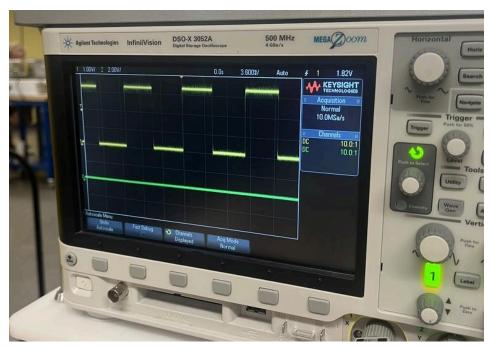

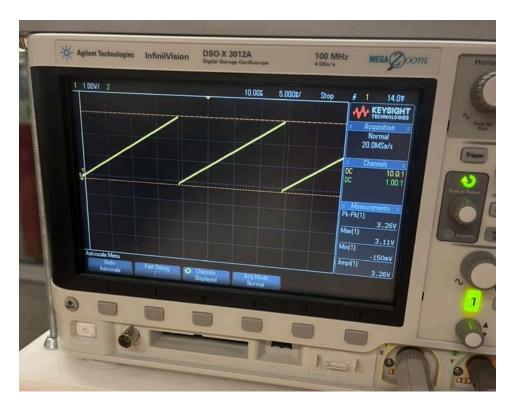

Above figure displays the duty cycle output from comparator for the R2R ladder network

Above figure displays R2R\_out RAMP function feeding into '-' terminal of comparator

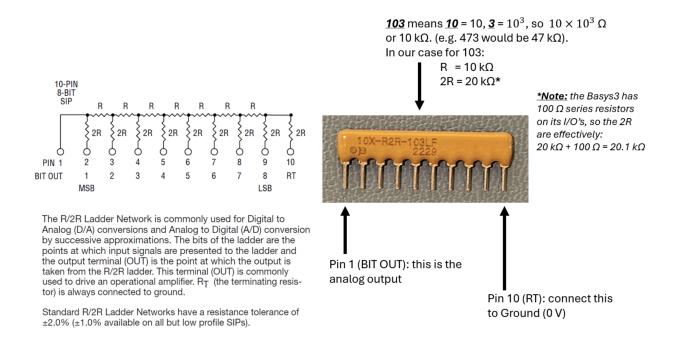

The second implementation of the custom analog-to-digital converter was done using a R2R ladder. Instead of feeding a sawtooth wave to the comparator using a pwm signal and a low pass filter, the comparator input is taken from the R2R ladder output resulting from the current binary pwm value. In other words, we supply the R2R\_OUT 8-bit bus containing our duty cycle to the 8 pins on the R2R ladder, and the output of the R2R ladder approximates this value using a resistor network. This works because a smaller binary value will need to pass through a larger quantity or resistors, therefore resulting in a larger voltage drop and therefore a smaller output voltage.

Here is the COMPARATOR\_R2R module below, which is the same as the PWM comparator module,

The only difference between the R2R and PWM operation is that rather than sending out an analog ramp voltage through the output of the BASYS board, we send out a discrete voltage (each bit is an analog HIGH or LOW voltage) and this passes through the R2R ladder network in order to become an analog ramp voltage. Then, the same operations occur (as explained above for PWM) in terms of comparisons

with the comparator and what occurs within the comparator module/waveform\_generator module. Below is a diagram to outline how the R2R and PWM signals are fed into the comparator,

#### **Successive FSM**

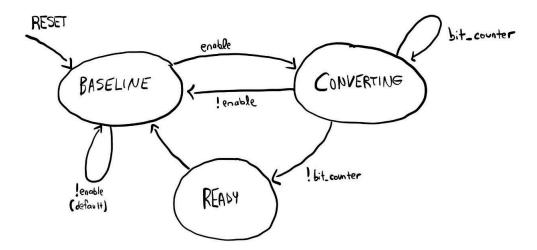

Below is the state diagram representing the logic/operation behind SuccessFSM module,

Above, we observe three states: BASELINE, CONVERTING, and READY. What happens is that by default, if lenable is true (enable comes from SUCCESSIVE\_ENABLED module, which is monitored by the logic of the selects, combinationally). If we have enabled as logic '1' or voltage 'HIGH,' then this will make the

next state CONVERTING; this allows for the start of the successive approximation algorithm to occur. When we enter into the CONVERTING state, then we set the bit\_counter to be 8 (this marks the number of bits we need to iterate through / compare).

```

99

BASELINE: begin

100

if (enable) begin

next_state = CONVERTING;

102

next_approximation = 8'b1000_0000;

next_bit_counter = WIDTH;

104

end

105

end

106

CONVERTING: begin

108

converting = 1;

109

if (bit counter == 0) begin

next_state = READY;

end else begin

113

if (!comp_input) begin

114

next_approximation = approximation_reg & ~(8'b00000001 << (bit_counter - 1));</pre>

next_approximation = next_approximation | (8'b000000001 << (bit_counter - 2));</pre>

119

next_bit_counter = bit_counter - 1;

end

end

```

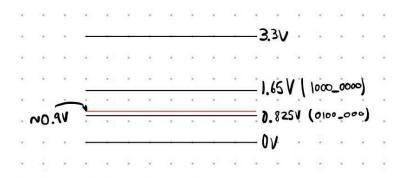

Based on the code from above, when we are in the CONVERTING state, we basically need to have an 'alarm' or 'notice' for when we should be done converting; this is when bit\_counter == 0. If bit\_counter == 0 then we have finished going through all the bits, and now this means our digital 'next\_approximation' value is ready to be processed through synchronizers and finally to be displayed as a RAW successive value. Besides this 'alarm' to notify the system when we should exit out of the CONVERTING state, the 'meat' of our operation occurs under the end else begin block. One important note is that during testing (will be discussed more below), we realized our successive approximation algorithm wasn't working with a 1 clock cycle update; this is because 'current\_duty\_cycle' (8 bits) needed more time than 1 clock period to process through waveform\_generator. So, we added a delay of 5000 cycles between each clock cycle such that updating occurs in the right way. Let us suppose the following situation to make the logic clear; let us suppose our analog input test voltage is approximately 0.9V, as denoted below

Initially, we will start with a reference voltage corresponding to 1000\_0000 (~1.65V). Remember, for the PREVIOUS 50 clock cycles, 'next\_approximation' held 1000\_0000, in the BASELINE state, but after 50 clock cycles, 'next\_approximation' got fed through our state register such that now 'approximation\_reg' now holds 1000\_0000 (please see more photos below for more information). What happens then is that the 'approximation\_reg' voltage value is compared with the analog input test voltage through the LM311 comparator. This is performed in the following way,

Our 8 bit 'next\_approximation' (this is the most up to date digital reference voltage value - we cannot use approximation\_reg, because it is lagged behind most up to date reference by one clock cycle) is fed

out from our SuccessiveFSM module and out through the PWM\_successive\_controller. With reference to the broader circuitry, 'next\_approximation' is defined as 'current\_duty\_cycle.' This value is fed into the waveform\_generator module such that an analog 'pwm\_out' value is generated from the 8 bit 'current\_duty\_cycle' value. The logic of the selects entering the waveform\_generator module allow the module to know when we have successive vs regular pwm and thus performing the correct functions. In this case, when we have (0111 - raw binary pwm successive), we only pass through the 'current\_duty\_cycle' value through the pwm\_inst module (which converts it to a duty cycle). Then, the duty cycle is fed through the LPF so it becomes a smoothed analog signal that can be compared with the analog input test voltage. After a comparison is made by the LM311, we get a comparator output that will be either '1' or '0.'

Coming back to our example from above (using 0.9V as analog input test voltage), for the first comparison we will have that the analog input voltage of 'current\_duty\_cycle' will be ~1.6V; therefore, for the first comparison, we get a logic '0' or voltage 'LOW' coming out of the LM311 comparator. This is then fed back into the SuccessiveFSM as 'PWM\_duty\_in' (see above figure) such that the value of PWM\_duty\_in can be used for the logic of the algorithm embedded in SuccessiveFSM. From our code above, the following statements will execute,

```

if (!comp_input) begin

next_approximation = approximation_reg & ~(8'b00000001 << (bit_counter - 1));

end</pre>

```

Since !comp\_input holds (comparator output will be logic '0'), we make the next\_approximation go from 1000\_0000 -> 0000\_0000. This works through the operation above,

```

1000 0000 & 0111 0000 -> 0000 0000

```

Then, right after the above logic branch, if we still have more bits to process (that is, we aren't yet at the LSB), we will, by *default*, set the next bit 'in line' to be a logic '1.'

```

if (bit_counter > 1) begin

next_approximation = next_approximation | (8'b00000001 << (bit_counter - 2));

end

next_bit_counter = bit_counter - 1;</pre>

```

This will mean that 'current\_duty\_cycle' and next\_approximation will have a value of  $0100_0000$  (this is for the same clock cycle for which we said next\_approximation ->  $0000_0000$ ). Thus, within that clock, 'current\_duty\_cycle' ->  $0100_0000$ . Then, this will be processed through waveform\_generator and be compared with the LM311. After ~5000 clock period delay (next clock cycle), our comparator output value is ready to be processed and will be used again for the logic. Now, since  $0100_0000 -> 0.825V <$

0.9V -> comparator output will be logic '1' or voltage 'HIGH.' So, now, the first 'if' logical branch will be skipped and thus we will keep the current bit as logic '1'; i.e., 0100\_0000 remains true for 'current\_duty\_cycle.' After, since we're not yet at LSB, we make the next bit a logic '1' through the above logical branch; we have,

Next\_approximation = 0100\_0000 | 0010\_0000 -> 0110\_0000

This whole process repeats in the same manner until we eventually converge to a 'next\_approximation' value that best approximates our analog input test voltage. At that point, we exit out of the CONVERTING state (when !bit\_counter holds) and enter the READY state. This is when we output our finalized 8 bit reference voltage, and this 8 bit value is what is displayed on the seven segment as the RAW value. Note that this whole process applies also to R2R.

## **Creative Design**

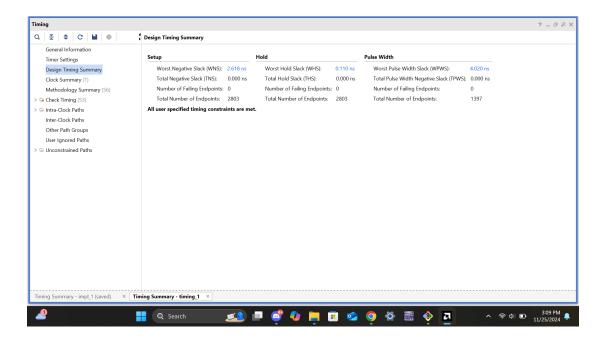

For the creative design option, we chose to increase the clock frequency to 200MHz from 100MHz (5%) and also add in an FSM for the menu module rather than just a plain mux (5%, what Dr. Onen mentioned in person). We also decided to solder our PWM, R2R and XADC circuits onto a Perfboard to ensure that it would look neat and wouldn't have any loose connections (10%). The implementation results are posted below for the first option showing that our WNS > 0 and was within an acceptable range (~2.618ns). The resource usage is also outlined below. The menu FSM was outlined previously (see 'menu FSM' section above outlining how the FSM was integrated).

For 2.618 ns WNS and 200 MHz clock:

Max clack frequency =

$$\frac{1}{\text{clock period} - \text{WNS}}$$

Max clack  $f = \frac{1}{\text{Sns} - 2.618 ns}$   $\frac{\alpha}{\text{Mox clock}}$   $\frac{1}{\text{Sns} - 2.618 ns}$   $\frac{\alpha}{\text{Mox period}}$   $\frac{1}{\text{Sns} - 2.618 ns}$   $\frac{1}{\text{Sns} - 2.618 ns}$   $\frac{1}{\text{Sns} - 2.618 ns}$   $\frac{1}{\text{Sns} - 2.618 ns}$   $\frac{1}{\text{Sns} - 2.618 ns}$

## <u>R2R</u>

## **PWM and XADC**

# **External circuit**

## AI tool use

We did end up using AI to help us design the whole system. However, most of the usage stemmed from a matter of helping us save time and streamline operations. This means that we all collectively understood what was going on. Moreover, AI ended up only being good at designing single modules or 'parts,' but not so great at 'putting the parts together.' So, the overall system design was done by us, but the design of the 'parts' of the system was done by AI (some). Also, all the logic for the selects (see introduction for all the selects and how they route to the modes) was developed by us and was developed efficiently through usage of *Karnaugh maps* (learned in ENEL 353).

# **Implementation Results**

Timing Results for 200MHz clock frequency (part of 5% bonus):

#### Utilization of FPGA:

# **Testing of Design Requirements**

For the type of testing, we carried out unit testing for each of the modes "PWM regular," "XADC," etc. Overall, all of the unit testing compromises overall system testing. Throughout our entire project, we implicitly carried out regression testing by testing code via changes with the circuit. It was not required to write testbenches for the code of the selects as we tested this after we programmed the code to the BASYS and tested the selects externally.

| Item                                                    | Checked/Not Checked                                                                        |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------|

| PWM Regular Mode (raw, avg, scaled)                     | All checked (raw, avg, scaled)                                                             |

| 2) R2R Regular Mode (raw, avg, scaled)                  | All checked (raw, avg, scaled)                                                             |

| 3) XADC (raw, avg, scaled)                              | All checked (raw, avg, scaled)                                                             |

| 4) PWM Successive (raw, avg, scaled)                    | All checked (raw, avg, scaled)                                                             |

| 5) R2R Successive (raw, avg, scaled)                    | All checked (raw, avg, scaled)                                                             |

| 6) Low pass filters for all systems                     | See below figure                                                                           |

| Stability of seven segment display for all the systems. | Very stable (completely stable at best to minimal flickering of ones place digit at worst) |

| Testing Documentation:                               | L |

|------------------------------------------------------|---|

|                                                      |   |

| >For PWM regular modes (0111,0101,6100):             | L |

| -> Use NIONF cop. for LPF (worked best)              |   |

| -) Use internal resistance of ISASYS!                |   |

| 7 For XAUC made (ODII, ODIO, OII)                    |   |

| -> Things worked good with a cap. range of for F-12F |   |

| (Parsa the Phone)                                    |   |

| -> For RZR regular                                   | ļ |

| > low ap. for LAF (NIONE) / Or even no cop. !        |   |

| -> For PWM successive (binary)                       | - |

| -> Jat cop. without well.                            | ŀ |

| (KSR 105K copositar)                                 | L |

| -> For RZR successive                                | ŀ |

| -> LOW cap. works hell!                              | L |

| (order of NF-) INF workered for us:)                 |   |

|                                                      | L |

|                                                      |   |

# **Conclusion**

Overall, we collectively designed a full ADC system that entailed multiple methods (successive PWM, regular R2R, etc.). All of the knowledge that we learned throughout the semester was used to apply towards this project and to create something tangible. Some next steps include *extending* this project in the future (perhaps for a masters project) to integrate a flash ADC algorithm or delta-sigma algorithm, or something more advanced.

## **Appendix 1: Code and XDC**

#### Pasted in order of hierarchy below:

```

module top level (

input logic clk,

// White space and comments used consistently throughout

code.

input logic reset,

// Input/Output names changed according to their functionality.

input logic [11:0] switches inputs,

// Logic input to convert between BCD/hex; note that by

input logic hex bin,

default things will be displayed in BCD (see inside seven segment module).

// 4 total selects below enable for 2<sup>4</sup> = 16 options; note that

input logic first select,

the selects are gray coded to optimize timing between sub-modes (e.g., R2R avg -> R2R avg &

scaling)

input logic second select.

// NOTE: Karnaugh maps were used to determine the

effecient combinational logic needed to 'encode' these selects

input logic third select,

input logic fourth select,

input

vauxp15,

// XADC inputs

input

vauxn15,

input

PWM duty in,

input logic r2r binary scaled enable,

input

R2R_duty_in,

output logic CA, CB, CC, CD, CE, CF, CG, DP, // These control which panel is ON for each

digit.

output logic AN1, AN2, AN3, AN4,

// These control the current four each of four digits in

seven seg.

output logic [15:0] led,

// Simple LEDs; these are used for successive output.

output logic pwm_waveform_out,

// PWM waveform output

output logic [7:0] R2R waveform out // R2R waveform output

);

// Internal signal declarations

logic [2:0] mode select;

logic [7:0] for_seven_seg;

logic pwm out;

logic [7:0] R2R out;

logic [15:0] led;

logic

ready;

logic [7:0]

V analog in;

logic [7:0]

V_analog_in_r2r;

```

```

logic [15:0] data;

logic [15:0] scaled_adc_data;

logic [7:0] r2r_comparator_result;

logic [11:0] r2r avg data;

logic [15:0] r2r_scaled_data;

logic [15:0] ave xadc;

logic [15:0] pwm scaled data;

logic [11:0] pwm_ave_data;

logic [6:0] daddr in;

logic [7:0] duty_cycle;

logic

enable;

logic

eos out;

logic

zero;

logic [7:0] r2r_successive_out;

logic

busy out;

logic

ready_pulse;

logic [15:0] bcd value, mux out;

logic [7:0] comparator result;

logic [7:0] pwm_successive_out;

logic r2r enable; //buzzer enable;

logic pwm enable;

logic pwm_out_internal;

logic pwm out int;

logic [7:0] current_reference;

logic enable_pwm_successive;

logic enable r2r successive;

logic [7:0] R2R_out_internal;

//logic [1:0] buzzer mode; // New signal for buzzer mode control

logic triangle_en;

logic [7:0] current R2R value;

logic [7:0] captured_pwm_successive;

logic [7:0] R2R_output;

logic [7:0] PWM_output;

// Constants

localparam CHANNEL_ADDR = 7'h1f;

assign mode_select = {third_select, fourth_select}; // iterative test

```

```

assign led[7:0] = captured pwm successive;

assign led[10] = pwm_waveform_out;

assign led[9] = PWM_duty_in;

successive on controller SUCCESSIVE ENABLED (

.fourth select(fourth select),

.third select(third select),

.second select(second select),

.down_button(r2r_binary_scaled_enable),

.first select(first select),

.enable_pwm_successive(enable_pwm_successive),

.enable_r2r_successive(enable_r2r_successive)

);

pwm_sar_controller PWM_successive_controller (

.clk(clk),

.reset(reset),

//.converting(converting),

.enable(enable pwm successive),

//.for_seven_seg(for_seven_seg),

.PWM duty in(PWM duty in),

//.all_states(all_states),

.current duty cycle(current reference),

//.bit counter(bit counter),

.captured_duty_cycle(captured_pwm_successive)

//.done(1'b0)

);

binary_regular_filter BINARY_REG_FILTER (

.fourth select(fourth select),

.third select(third select),

.second_select(second_select),

.first_select(first_select),

.V analog in r2r(V analog in r2r),

.comparator_result(comparator_result),

```

```

.r2r_successive_out(r2r_successive_out),

.captured pwm successive(captured pwm successive),

.down button(r2r binary scaled enable),

.R2R_output(R2R_output),

.PWM output(PWM output)

);

r2r sar controller R2R successive controller (

.clk(clk),

.reset(reset),

.enable(enable_r2r_successive), // leave as 0 for now, deal with logic later.

.R2R duty in(R2R duty in),

.current value internal(current R2R value),

.captured R2R value(r2r successive out),

.done(1'b0)

);

comparator COMPARATOR (

.clk(clk),

.reset(reset).

.comparator_output(PWM_duty_in),

.current duty cycle(R2R out internal),

.captured duty cycle(comparator result)

);

comparator COMPARATOR R2R (

.clk(clk),

.reset(reset),

.comparator_output(R2R_duty_in),

.current_duty_cycle(R2R_out_internal),

.captured_duty_cycle(V_analog_in_r2r)

);

// XADC Instantiation

xadc wiz 0 XADC INST (

.di in(16'h0000),

.daddr in(CHANNEL ADDR),

.den_in(enable),

.dwe in(1'b0),

.drdy out(ready),

.do_out(data),

.dclk_in(clk),

.reset in(reset),

.vp_in(1'b0),

```

```

.vn_in(1'b0),

.vauxp15(vauxp15),

.vauxn15(vauxn15),

.channel_out(),

.eoc_out(enable),

.alarm_out(),

.eos_out(eos_out),

.busy_out(busy_out)

);

// Instantiate the FSM

FSM_parent parent (

.clk(clk),

.reset(reset),

.first_select(first_select),

.second select(second select),

.third_select(third_select),

.down_button(r2r_binary_scaled_enable),

.fourth select(fourth select),

.triangle_en(triangle_en),

.pwm_enable(pwm_enable),

.r2r enable(r2r enable)

);

r2r_processing R2R_PROC (

.clk(clk),

.reset(reset),

.data(R2R output),

.ave_data(r2r_avg_data),

.scaled_r2r_data(r2r_scaled_data)

);

// PWM ADC instance (internally timed)

pwm_adc_processing PWM_ADC (

.clk(clk),

.reset(reset),

.pwm in(PWM output),

.ave_data(pwm_ave_data),

.scaled_adc_data(pwm_scaled_data),

.conversion done()

// Connect if needed

);

```

```

r2r_pwm_waveform_enable ALL_THREE_MUX (

.r2r_enable(r2r_enable),

.pwm out internal(pwm out internal),

.pwm enable(pwm enable),

.R2R out internal(R2R out internal),

.scaled adc data(scaled adc data),

//.led(led[15:0]),

.pwm_out(pwm_waveform_out),

.R2R out(R2R waveform out)

);

// Rest of your existing module instantiations

adc_processing ADC_PROC (

.clk(clk),

.reset(reset),

.ready(ready),

.data(data),

.ave_data(ave_xadc),

.scaled adc data(scaled adc data)

//.ready pulse(ready pulse)

);

logic [3:0] decimal_pt;

menu_FSM menu_module (

.scaled_adc_data(scaled_adc_data),

// Avg. + Scaled XADC

.ave xadc(ave xadc),

// Avg. XADC

.xadc_raw(data[15:4]),

// XADC raw

.pwm raw(comparator result),

// PWM raw

.reg_switches_in(switches_inputs),

// switches

.r2r raw(V analog in r2r),

// r2r raw

.pwm_avg(pwm_ave_data),

// pwm avg. data

.pwm scaled(pwm scaled data),

// pwm scaled

.r2r_avg(r2r_avg_data),

.r2r scaled(r2r scaled data),

.pwm successive raw(captured pwm successive), //binary approximation start:

.r2r_successive_raw_in(r2r_successive_out),

.clk(clk),

.rst(reset),

```

```

.first select(first select).

// LOGICAL selects to CHOOSE what passes through to

seven segment module (i.e., what selects between say, scaled adc data or ave xadc, etc.)

.second select(second select),

.third select(third select),

.fourth select(fourth select),

.down_button_select(r2r_binary_scaled_enable),

.mux out(mux out),

// This will get outputted to the seven segment module.

.decimal point(decimal pt)

);

seven segment display subsystem SEVEN SEGMENT DISPLAY (

.clk(clk),

.hex_bin(hex_bin),

.first select(first select),

// The selects feed in here in order to aid with the logic of

making the segment all zeros.

.second select(second select),

.third select(third select),

.fourth_select(fourth_select),

.reset(reset),

.mux_in(mux_out),

.decimal point(decimal pt),

.CA(CA), .CB(CB), .CC(CC), .CD(CD),

.CE(CE), .CF(CF), .CG(CG), .DP(DP),

.AN1(AN1), .AN2(AN2), .AN3(AN3), .AN4(AN4)

);

waveform_generator #(

.WIDTH(8),

.CLOCK_FREQ(200_000_000),

// 200MHz clock (5% bonus)

.WAVE FREQ(100)

// Frequency set to 100 Hz to ensure averager module

outputs good values.

) waveform generator (

.clk(clk),

.reset(reset),

.enable(triangle en),

.current reference(current reference), //digitized reference feeding in

// selects for combinational logic

.first_select(first_select),

.second select(second select),

.third_select(third_select),

```

```

.fourth_select(fourth_select),

.r2r binary scaled enable(r2r binary scaled enable),

.current reference r2r(current R2R value),

.pwm_out(pwm_out_internal),

.R2R_out(R2R_out_internal)

);

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/20/2024 04:00:01 PM

// Design Name:

// Module Name: successive_on_controller

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

II

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// Module contains combinational logic for the enables for successive R2R and PWM depending

upon the four selects and the down button.

module successive on controller(

// Logical controller designed to engage in abstraction for

successive controllers.

input logic fourth select,

input logic third select,

input logic second select,

input logic first select,

input down_button,

// Extra button because we have 17 options with successive

added.

output logic enable_pwm_successive,

```

```

output logic enable_r2r_successive

logic enable pwm successive;

logic enable_r2r_successive;

// Logic below controls the successive enables for R2R and PWM.

assign enable pwm successive = (fourth select & second select & ~first select) |

(fourth select & ~third select & ~first select) | (fourth select & third select & second select &

~first select);

assign enable_r2r_successive = (fourth_select & ~third_select & first_select) | (down_button);

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/20/2024 02:49:58 PM

// Design Name:

// Module Name: pwm sar controller

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// Controller below 'controls' PWM SAR routing - The PWM duty in is continuously fed into this

module such that continuous comparisons in SuccessiveFSM occurs.

// The 'meat' of the logic for successive is embedded in the SuccessiveFSM file.

module pwm_sar_controller #(

parameter WIDTH = 8

)(

input logic clk,

// Input signals.

```

```

input logic reset,

input logic enable,

input logic PWM duty in,

// This comes from comparator (either will be 1 or 0;

1 if analog input test > reference duty voltage, else a 0)

output logic [WIDTH-1:0] current duty cycle, // This is the intermediate reference voltage

that is used for the approximation algorithm (1000 0000 -> 0100 0000 -> 0110 0000 -> ETC.);

We do NOT use this for the seven segment output, because they are strictly intermediate

values.

output logic [WIDTH-1:0] captured duty cycle // THIS is the value we use for the seven

segement display as it is the 'ready' state digital reference voltage coming from SuccessiveFSM!

);

logic [WIDTH-1:0] current value internal;

// Intermediate signals.

logic [WIDTH-1:0] for seven seg;

logic done;

// Instantiate SAR ADC

SuccessiveFSM #(

.WIDTH(WIDTH)

) SuccessiveFSM (

.clk(clk),

.reset(reset),

.enable(enable),

.comparator(PWM_duty_in),

.next approximation(current value internal),

.digitized successive(for seven seg),

.done(done)

);

// Added a sync below to allow for more stable output values going into seven segment

display.

always_ff @(posedge clk) begin

if (reset) begin

captured duty cycle <= '0;

end else if (done) begin

captured_duty_cycle <= for_seven_seg;

end

end

// Pure combinational assignment for current value

assign current_duty_cycle = current_value_internal;

endmodule

```

```

`timescale 1ns / 1ps

// Company:

// AUTHOR: Evan Barker

// Create Date: 11/20/2024 02:26:07 PM

// Design Name:

// Module Name: SuccessiveFSM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

module SuccessiveFSM #(

parameter WIDTH = 8

)(

input logic clk,

input logic reset,

input logic enable,

input logic comparator,

output logic [WIDTH-1:0] next_approximation,

output logic [WIDTH-1:0] digitized_successive,

output logic done

//output logic converting,

//output logic [2:0] all_states

//output logic [WIDTH-1:0] test value,

// output logic [3:0] bit_position,

//output logic comp_input

);

typedef enum logic [2:0] {

BASELINE = 3'b001,

CONVERTING = 3'b010,

READY

= 3'b100

} state type;

```

```

state_type state, next_state;

logic [WIDTH-1:0] approximation reg, next approximation;

logic [3:0] bit counter, next bit counter;

logic [WIDTH-1:0] digitized_reg;

logic converting;

// Counter for 50 clock cycles

logic [12:0] delay_counter;

assign comp input = comparator;

assign bit position = bit counter;

//ssign test value = approximation reg;

//assign all states = state;

// Simple 50-cycle counter

always_ff @(posedge clk) begin

if (reset) begin

delay counter <= 0;

end else begin

if (delay_counter == 4999) // Count 0 to 49 = 50 cycles

delay counter <= 0;

else

delay counter <= delay counter + 1;

end

end

// Sequential logic - only update when counter hits 49

always_ff @(posedge clk) begin

if (reset) begin

state <= BASELINE;

approximation reg <= 8'b0000 0000;

bit counter <= 4'b1000;

digitized_reg <= 8'b0000_0000;

end else if (delay counter == 4999) begin // Update every 50 cycles

state <= next state;

approximation reg <= next approximation;

bit_counter <= next_bit_counter;

if (state == READY) begin

digitized_reg <= approximation_reg;</pre>

end

end

end

assign digitized_successive = digitized_reg;

```

```

// Combinational logic remains the same

always_comb begin

next_state = state;

next_approximation = approximation_reg;

next_bit_counter = bit_counter;

converting = 0;

done = 0;

case (state)

BASELINE: begin

if (enable) begin

next_state = CONVERTING;

next_approximation = 8'b1000_0000;

next_bit_counter = WIDTH;

end

end

CONVERTING: begin

converting = 1;

if (bit_counter == 0) begin

next state = READY;

end else begin

if (!comp input) begin

next_approximation = approximation_reg & ~(8'b00000001 << (bit_counter - 1));</pre>

end

if (bit_counter > 1) begin

next_approximation = next_approximation | (8'b00000001 << (bit_counter - 2));</pre>

end

next bit counter = bit counter - 1;

end

end

READY: begin

done = 1;

next state = BASELINE;

next bit counter = WIDTH;

end

default: next state = BASELINE;

endcase

```

```

if (reset) begin

next state = BASELINE;

next_approximation = '0;

next bit counter = WIDTH;

end

if (!enable && state != BASELINE) begin

next state = BASELINE;

end

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

// Create Date: 11/22/2024 10:19:51 PM

// Design Name:

// Module Name: binary_regular_filter

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// A bit motive for why this module/filter was created was to engage in the practice of 'reusability'

for the AVERAGED and SCALED modules!

// Instead of adding FOUR extra modules in total for R2R and PWM successive for their

averaging and scaling, we can just make use of what we have so far and just implement this

filter!

```

```

module binary_regular_filter(

// This 'filter' selects between either REGULAR or

SUCCESSIVE for the RAW output values that feed into the AVERAGED and SCALED modules.

input logic [7:0] V analog in r2r,

// R2R REGULAR

input logic [7:0] comparator_result,

// PWM REGULAR

input logic [7:0] r2r successive out,

// R2R SUCCESSIVE

input logic [7:0] captured_pwm_successive,

// PWM SUCCESSIVE

input logic fourth select.

// SELECTs used for the logic.

input logic third select,

input logic second select,

input logic first select,

input logic down button,

output logic [7:0] R2R output,

// Either SUCCESIVE or REGULAR outputs for the

below two outputs.

output logic [7:0] PWM_output

);

logic [7:0] R2R_output;

logic [7:0] PWM output;

logic r2r reg enable;

logic r2r successive enable;

logic pwm reg enable;

logic pwm successive enable;

assign r2r reg enable = (fourth select & third select & ~second select) | (fourth select &

third select & first select);

assign r2r successive enable = (fourth select & ~third select & first select) | (down button);

assign pwm_reg_enable = (~fourth_select & third_select & ~second_select) | (~fourth_select

& third select & first select);

assign pwm successive enable = (fourth select & second select & ~first select) |

(fourth select & ~third select & ~first select) | (fourth select & third select & second select &

~first_select);

always_comb begin

if (r2r reg enable)

R2R output = V analog in r2r;

else if (r2r successive enable)

R2R output = r2r successive out;

else

// IMPORTANT: This else block was necessary to prevent

inferred latches!

```

```

R2R_output = 8'h00;

end

always_comb begin

if (pwm_reg_enable)

PWM output = comparator result;

else if (pwm successive enable)

PWM_output = captured_pwm_successive;

else

PWM_output = 8'h00;

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/20/2024 02:50:41 PM

// Design Name:

// Module Name: r2r_sar_controller

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// R2R SAR ADC Controller with One-Hot Encoded FSM

module r2r sar controller #(

parameter WIDTH = 8

)(

input logic clk,

input logic reset,

input logic enable,

```

```

input logic R2R_duty_in,

output logic [WIDTH-1:0] current value internal,

output logic [WIDTH-1:0] captured R2R value,

output logic done

);

logic converting;

logic comparator sync;

logic [WIDTH-1:0] current R2R value;

// Two-stage synchronizer for comparator input with reset

// logic comp sync1;

//

always ff @(posedge clk) begin

//

if (reset) begin

//

comp sync1 \leq 0;

comparator_sync <= 0;

//

//

end else begin

comp sync1 <= R2R duty in;

//

//

comparator_sync <= comp_sync1;</pre>

//

end

//

end

// Instantiate base SAR ADC

SuccessiveFSM #(

.WIDTH(WIDTH)

) SuccessiveFSM (

.clk(clk),

.reset(reset),

.enable(enable),

.comparator(R2R_duty_in),

.digitized successive(current R2R value),

.next approximation(current value internal),

.done(done)

//.converting(converting)

);

// Mealy-style output logic

// Replace combinational block with sequential for captured value

always ff @(posedge clk) begin

if (reset) begin

captured R2R value <= '0;

end else if (done) begin

captured_R2R_value <= current_R2R_value;

end

end

```

```

// Pure combinational assignment for current value

//assign current_R2R_value = current_value_internal;

endmodule

`timescale 1ns / 1ps

// Company:

// AUTHOR: Evan Barker

// Create Date: 11/20/2024 02:26:07 PM

// Design Name:

// Module Name: SuccessiveFSM

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module SuccessiveFSM #(

parameter WIDTH = 8

)(

input logic clk,

input logic reset,

input logic enable,

input logic comparator,

output logic [WIDTH-1:0] next_approximation,

output logic [WIDTH-1:0] digitized successive,

output logic done

//output logic converting,

//output logic [2:0] all states

//output logic [WIDTH-1:0] test value,

// output logic [3:0] bit_position,

//output logic comp input

);

```

```

typedef enum logic [2:0] {

BASELINE = 3'b001.

CONVERTING = 3'b010,

READY

= 3'b100

} state type;

state_type state, next_state;

logic [WIDTH-1:0] approximation reg, next approximation;

logic [3:0] bit counter, next bit counter;

logic [WIDTH-1:0] digitized reg;

logic converting;

// Counter for 50 clock cycles

logic [12:0] delay_counter;

assign comp_input = comparator;

assign bit_position = bit_counter;

//ssign test value = approximation reg;

//assign all states = state;

// Simple 50-cycle counter

always_ff @(posedge clk) begin

if (reset) begin

delay counter <= 0;

end else begin

if (delay counter == 4999) // Count 0 to 49 = 50 cycles

delay counter <= 0;

else

delay counter <= delay counter + 1;

end

end

// Sequential logic - only update when counter hits 49

always ff @(posedge clk) begin

if (reset) begin

state <= BASELINE;

approximation_reg <= 8'b0000_0000;

bit counter <= 4'b1000;

digitized reg <= 8'b0000 0000;

end else if (delay counter == 4999) begin // Update every 50 cycles

state <= next state;

approximation_reg <= next_approximation;

bit_counter <= next_bit_counter;

if (state == READY) begin

```

```

digitized_reg <= approximation_reg;</pre>

end

end

end

assign digitized successive = digitized reg;

// Combinational logic remains the same

always_comb begin

next state = state;

next_approximation = approximation_reg;

next bit counter = bit counter;

converting = 0;

done = 0;

case (state)

BASELINE: begin

if (enable) begin

next_state = CONVERTING;

next approximation = 8'b1000 0000;

next_bit_counter = WIDTH;

end

end

CONVERTING: begin

converting = 1;

if (bit counter == 0) begin

next_state = READY;

end else begin

if (!comp input) begin

next_approximation = approximation_reg & ~(8'b00000001 << (bit_counter - 1));</pre>

end

if (bit counter > 1) begin

next_approximation = next_approximation | (8'b00000001 << (bit_counter - 2));</pre>

end

next_bit_counter = bit_counter - 1;

end

end

READY: begin

done = 1;

```

```

next_state = BASELINE;

next_bit_counter = WIDTH;

end

default: next_state = BASELINE;

endcase

if (reset) begin

next_state = BASELINE;

next_approximation = '0;

next_bit_counter = WIDTH;

end

if (!enable && state != BASELINE) begin

next_state = BASELINE;

end

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/13/2024 10:30:15 PM

// Design Name:

// Module Name: comparator

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

```

// Comparator module below functions to 'capture' the falling edge of the duty cycle output from comparator for PWM RAMP

// For the purpose of reusability, we used this module also for R2R!

// Essentially, right when the analog input test voltage intersects with the ramp, for the time thereafter the comparator output voltage will be a zero. Thus, we detect WHEN the comparator output will be zero; the 8 bit binary value corresponding to this matches the PWM RAW input.

```

module comparator

#(

parameter int WIDTH = 8

input logic clk,

input logic reset,

input logic comparator output,

input logic [WIDTH-1:0] current duty cycle,

output logic [WIDTH-1:0] captured_duty_cycle

);

// Synchronization registers

logic comp sync1, comp sync2;

logic comparator_output_prev;

// Noise filtering counter

logic [3:0] stable_counter;

logic [WIDTH-1:0] temp capture;

always ff @(posedge clk) begin

if (reset) begin

comp_sync1 <= 1'b1;

comp sync2 <= 1'b1;

comparator_output_prev <= 1'b1;

captured duty cycle <= '0;

stable counter <= '0;

end else begin

// Two-stage synchronization

comp sync1 <= comparator output;

comp sync2 <= comp sync1;</pre>

comparator_output_prev <= comp_sync2;

// Falling edge detection with noise filtering

if (comparator_output_prev && !comp_sync2) begin

```

```

temp_capture <= current_duty_cycle;</pre>

stable counter <= 4'hF; // Start stability check

end else if (stable counter > 0) begin

stable_counter <= stable_counter - 1;

if (stable counter == 1) begin

captured duty cycle <= temp capture;

end

end

end

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/13/2024 10:30:15 PM

// Design Name:

// Module Name: comparator

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

```

// Comparator module below functions to 'capture' the falling edge of the duty cycle output from comparator for PWM RAMP

// For the purpose of reusability, we used this module also for R2R!

// Essentially, right when the analog input test voltage intersects with the ramp, for the time thereafter the comparator output voltage will be a zero. Thus, we detect WHEN the comparator output will be zero; the 8 bit binary value corresponding to this matches the PWM RAW input.

module comparator

```

#(

parameter int WIDTH = 8

)

input logic clk,

input logic reset,

input logic comparator output,

input logic [WIDTH-1:0] current duty cycle,

output logic [WIDTH-1:0] captured duty cycle

);

// Synchronization registers

logic comp_sync1, comp_sync2;

logic comparator output prev;

// Noise filtering counter

logic [3:0] stable counter;

logic [WIDTH-1:0] temp_capture;

always ff @(posedge clk) begin

if (reset) begin

comp sync1 <= 1'b1;

comp_sync2 <= 1'b1;

comparator_output_prev <= 1'b1;

captured duty cycle <= '0;

stable counter <= '0;

end else begin

// Two-stage synchronization

comp_sync1 <= comparator_output;</pre>

comp sync2 <= comp sync1;</pre>

comparator output prev <= comp sync2;

// Falling edge detection with noise filtering

if (comparator_output_prev && !comp_sync2) begin

temp capture <= current duty cycle;

stable_counter <= 4'hF; // Start stability check

end else if (stable counter > 0) begin

stable counter <= stable counter - 1;

if (stable counter == 1) begin

captured duty cycle <= temp capture;

end

end

end

end

```

## endmodule

```

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/06/2024 11:47:22 AM

// Design Name:

// Module Name: FSM_parent

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

module FSM_parent(

input logic clk,

input logic reset,

input logic first_select,

// LOGICAL SELECTS

input logic second_select,

input logic third select,

input logic fourth_select,

input down_button,

output logic triangle_en,

// OUTPUTS: 1 enable ON when either r2r_enable is true OR

pwm_enable is true (either). Feeds into downcounter/pwm_inst.

output logic r2r_enable,

output logic pwm_enable

);

// Intermediate signals:

logic pwm_enable;

logic r2r_enable;

logic triangle en;

logic first_mode_select;

```

```

logic second_mode_select;

logic [1:0] mode select;

// input logic for selects that dictate mode_select values (R2R or PWM).

assign first mode select = (fourth select & third select & ~second select) | (fourth select &

first select) | (down button);

assign second mode select = (~fourth select & third select & first select) | (~fourth select

& third select & ~second select) | (fourth select & ~third select & ~first select) | (fourth select

& third select & second select & ~first select);

assign mode_select = {first_mode_select, second_mode_select};

output mode fsm FSM (

.clk(clk),

.reset(reset),

.mode_select(mode_select),

.pwm enable(pwm enable),

.r2r_enable(r2r_enable)

);

assign triangle_en = pwm_enable | r2r_enable;

endmodule

module output_mode_fsm (

input logic clk,

input logic reset,

input logic [1:0] mode_select, // Two-bit input for mode selection

output logic pwm enable,

output logic r2r_enable

);

typedef enum logic [1:0] {

OFF_MODE = 2'b00,

PWM MODE = 2'b01,

R2R MODE = 2'b10

} statetype;

statetype current state, next state;

// State register

always ff @(posedge clk or posedge reset) begin

if (reset)

current state <= OFF MODE;

else

current_state <= next_state;

```

```

end

// Next state logic

always_comb begin

next_state = statetype'(mode_select); // Directly use mode_select as the next state

end

// Output logic

always_comb begin

pwm enable = 0;

r2r_enable = 0;

case (current_state)

PWM_MODE: pwm_enable = 1;

R2R MODE: r2r enable = 1;

OFF_MODE: ; // All outputs remain 0

endcase

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

// Create Date: 11/10/2024 10:48:15 PM

// Design Name:

// Module Name: r2r_processing

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

module r2r_processing #(

parameter int SCALING FACTOR = 3400,

// Direct voltage scaling

parameter int SHIFT_FACTOR = 8, // Adjusted to prevent premature clamping

```

```

parameter int INPUT_BITS = 8,

parameter int AVERAGE_POWER = 8

) (

input logic

clk,

input logic

reset,

input logic [7:0]

data,

output logic [15:0]

scaled_r2r_data,

output logic [11:0]

ave_data

);

// Internal signals

logic [7:0] ramp_counter;

logic

ready_pulse;

// Ensure enough width for multiplication

localparam int SCALE_WIDTH = 24; // Wide enough for multiplication

logic [SCALE_WIDTH-1:0] scaled_temp;

logic [11:0] averaged value;

// Timing control

always ff @(posedge clk) begin

if (reset)

ramp_counter <= '0;

else

ramp_counter <= ramp_counter + 1'b1;

end

always_ff @(posedge clk) begin

if (reset)

ready_pulse <= 1'b0;

else

ready pulse <= (ramp counter == 8'hFF);

end

// Averager instance

averager #(

.power(AVERAGE_POWER),

.N(INPUT BITS),

.M(INPUT_BITS + AVERAGE_POWER/2)

) AVERAGER (

.reset(reset),

.clk(clk),

.EN(ready_pulse),

.Din(data),

.Q(averaged_value)

```

```

);

assign ave_data = averaged_value;

// Pre-scaling normalization

logic [11:0] normalized value;

always comb begin

// Map input range (0-4095) to (0-255)

normalized value = averaged value >> 4;

end

// Scaling pipeline with adjusted range

always_ff @(posedge clk) begin

if (reset) begin

scaled_r2r_data <= '0;

scaled temp <= '0;

end

else if (ready_pulse) begin

// Scale normalized value to voltage range

scaled_temp <= normalized_value * SCALING_FACTOR;</pre>

// Limit output to 3300 (3.30V)

if ((scaled temp >> SHIFT FACTOR) > 16'd3300) begin

scaled_r2r_data <= 16'd3300;

end else begin

scaled r2r data <= scaled temp >> SHIFT FACTOR;

end

end

end

endmodule

module averager #(

parameter int power = 8, \frac{1}{2}8 = 256 samples

// Bit width of input data

parameter int N = 8,

parameter int M = N + power/2 // Output width with extra resolution bits

) (

input logic clk,

input logic reset,

input logic EN,

input logic [N-1:0] Din,

output logic [M-1:0] Q // Now M bits wide instead of N

```

);

```

// Declare register array and sum with proper widths

logic [N-1:0] REG ARRAY [2**power:1];

logic [power+N-1:0] sum; // Wide enough to hold full sum

// Take more bits from the sum to get the extra resolution

assign Q = sum[power+N-1:power/2]; // Changed bit selection for more resolution

always ff @(posedge clk) begin

if (reset) begin

sum <= '0;

for (int j = 1; j \le 2^* power; j++) begin

REG ARRAY[j] <= '0;

end

end

else if (EN) begin

// Update sum and shift register

sum <= sum + Din - REG ARRAY[2**power];</pre>

for (int j = 2^{**}power; j > 1; j--) begin

REG_ARRAY[j] <= REG_ARRAY[j-1];</pre>

end

REG_ARRAY[1] <= Din;</pre>

end

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/10/2024 09:56:19 PM

// Design Name:

// Module Name: pwm adc processing

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

```

## // Code works below

```

module pwm adc processing #(

parameter int SCALING FACTOR = 3400,

// Direct voltage scaling

parameter int SHIFT_FACTOR = 8,

// Adjusted to prevent premature clamping

parameter int INPUT BITS = 8,

parameter int AVERAGE POWER = 8

) (

input logic

clk,

input logic

reset,

input logic [7:0]

pwm in,

scaled adc data,

output logic [15:0]

output logic [11:0]

ave_data,

output logic

conversion_done

);

// Internal signals

logic [7:0] ramp_counter;

logic

ready_pulse;

// Ensure enough width for multiplication

localparam int SCALE WIDTH = 24; // Wide enough for multiplication

logic [SCALE_WIDTH-1:0] scaled_temp;

logic [11:0] averaged value;

// Timing control

always ff @(posedge clk) begin

if (reset)

ramp_counter <= '0;

else

ramp_counter <= ramp_counter + 1'b1;

end

always_ff @(posedge clk) begin

if (reset)

ready pulse <= 1'b0;

ready_pulse <= (ramp_counter == 8'hFF);</pre>

end

// Averager instance

averager #(

.power(AVERAGE_POWER),

```

```

.N(INPUT_BITS),

.M(INPUT_BITS + AVERAGE_POWER/2)

) AVERAGER (

.reset(reset),

.clk(clk),

.EN(ready_pulse),

.Din(pwm_in),

.Q(averaged_value)

);

assign ave_data = averaged_value;

// Pre-scaling normalization

logic [11:0] normalized value;

always_comb begin

// Map input range (0-4095) to (0-255)

normalized value = averaged value >> 4;

end

// Scaling pipeline with adjusted range

always_ff @(posedge clk) begin

if (reset) begin

scaled adc data <= '0;

scaled_temp <= '0;

conversion done <= 1'b0;

end

else if (ready_pulse) begin

// Scale normalized value to voltage range

scaled_temp <= normalized_value * SCALING_FACTOR;</pre>

if ((scaled temp >> SHIFT FACTOR) > 16'd3300) begin

scaled_adc_data <= 16'd3300;

end else begin

scaled adc data <= scaled temp >> SHIFT FACTOR;

end

conversion done <= 1'b1;

end

else begin

conversion done <= 1'b0;

end

end

endmodule

```

```

module averager #(

parameter int power = 8, // 2^8 = 256 samples

parameter int N = 8,

// Bit width of input data

parameter int M = N + power/2 // Output width with extra resolution bits

) (

input logic clk,

input logic reset,

input logic EN,

input logic [N-1:0] Din,

output logic [M-1:0] Q // Now M bits wide instead of N

);

// Declare register array and sum with proper widths

logic [N-1:0] REG_ARRAY [2**power:1];

logic [power+N-1:0] sum; // Wide enough to hold full sum

// Take more bits from the sum to get the extra resolution

assign Q = sum[power+N-1:power/2]; // Changed bit selection for more resolution

always_ff @(posedge clk) begin

if (reset) begin

sum <= '0;

for (int j = 1; j \le 2^*power; j++) begin

REG ARRAY[j] <= '0;

end

end

else if (EN) begin

// Update sum and shift register

sum <= sum + Din - REG ARRAY[2**power];

for (int j = 2^*power; j > 1; j--) begin

REG_ARRAY[j] <= REG_ARRAY[j-1];</pre>

end

REG_ARRAY[1] <= Din;</pre>

end

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/06/2024 02:58:21 PM

```

```

// Design Name:

// Module Name: all three muxes

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module r2r pwm waveform enable(

input logic pwm_out_internal,

input logic [7:0] R2R_out_internal,

input logic [15:0] scaled adc data,

input logic r2r_enable,

//input logic [15:0] led,

input logic pwm enable,

//input logic [7:0] R2R_out,

//output logic [15:0] led,

output logic pwm_out, //buzzer_out,

output logic [7:0] R2R_out

);

//logic [15:0] led;

//assign led = pwm_out_internal ? scaled_adc_data : '0;

always comb begin

pwm_out = pwm_enable ? pwm_out_internal : '0;

R2R out = r2r enable ? R2R out internal : '0;

end

endmodule

//`timescale 1ns / 1ps

// Company:

// Engineer:

//

```

```

// Create Date: 11/11/2024 11:56:43 AM

// Design Name:

// Module Name: adc processing

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

// Calculation: This scales FFFFh to 270Fh (i.e. 9999d)

// mVolts = ave data/(2^16 - 1) * 9999 = ave data * 0.152575

// mVolts \sim ave data * 1250/2^13 = (ave data) * 1250 >> 13

// NOTE: The 7-seg display will display in millivolts.

i.e. 9999 is 0.9999 V or 999.9 mV

// 3.300 instead of 0.9999!

place the decimal point in the correct place!

//scaled_adc_data <= (ave_data*1250) >> 13; // 1250/(2^13) ~ 0.15257495994506752117

//scaled adc data <= (ave data*79993) >> 19; // 9999/(2^{16} - 1) = 0.15257495994506752117

// 0.15257495994506752117 \sim 79993/2^19 (more accurate than

previous scaling)

// Perform the calculation with wider intermediate result to avoid 32-bit overflow error

// Since FFFF means we are at 3.300V, we can keep (2^16 -1) as part of above calc., but

instead multiply by 3300 (3.300) - add d.p. later.

// So, we get that, V = ave_data/(2^16-1) * 3300 = ave_data * 0.0503547723 ~ (ave_data * 52)

>> 10

module adc processing #(

parameter int SCALING FACTOR = 825,

// Default scaling factor changed because for

lab 7 we require 3.300V NOT 0.9999V/999.9mV

parameter int SHIFT FACTOR = 14

) (

input logic

clk,

input logic

reset,

input logic

ready,

input logic [15:0] data,

output logic [15:0] scaled_adc_data,

```

```

output logic [15:0] ave_data

//output logic

ready pulse

);

logic [15:0] ave_data;

logic

ready r;

logic [15:0] scaled adc data pipe;

// Calculate the bit width for the scaling factor

localparam int SCALING FACTOR WIDTH = $clog2(SCALING FACTOR) + 1;

// Calculate the intermediate width dynamically based on ave data (16-bits) and scaling factor

localparam int INTERMEDIATE WIDTH = 16 + SCALING FACTOR WIDTH;

// Define the intermediate register with the required bit width, to avoid 32-bit overflow on

intermediate calculation

logic [INTERMEDIATE_WIDTH-1:0] scaled_adc_data_temp;

// Pulser

always_ff @(posedge clk)

if (reset)

ready_r <= 0;

else

ready r <= ready;

assign ready pulse = ~ready r & ready; // generate 1-clk pulse when ready goes high

xadc averager #(

.power(8), // 2^{**}8 = 256 samples

.N(16) // Changed to match 12-bit ADC data

) XADC AVERAGER (

.reset(reset),

.clk(clk),

.EN(ready pulse),

.Din(data), // Take only the 12 MSBs of the XADC data

.Q(ave data) // Map to upper 12 bits of ave data

);

// Zero the lower bits

//assign ave data[3:0] = 4'b0000;

// averager #(

.power(8), // 2**(power) samples, default is 2**8 = 256 samples (4^4 = 256 samples, adds

4 bits of ADC resolution)

.N(16) // # of bits to take the average of

// ) AVERAGER (

```

```

//

.reset(reset),

//

.clk(clk),

//

.EN(ready_pulse),

//

.Din(data),

//

.Q(ave_data)

// );

always_ff @(posedge clk) begin

if (reset) begin

scaled adc data <= 0;

scaled adc data temp <= 0;

scaled adc data pipe <= 0;

end

else if (ready pulse) begin

scaled_adc_data_temp <= ave_data * SCALING_FACTOR;

// Use a wider temp

register to avoid 32-bit overflow error

scaled adc data pipe <= scaled adc data temp >> SHIFT FACTOR; // Shift right by

19 after the multiplication

scaled_adc_data

<= scaled_adc_data_pipe; // Additional register faciliates pipelining,</pre>

if needed, for

end

// higher clock frequencies. Costs are an additional

register

// and an additional 1 clk cycle latency.

end

endmodule

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 11/14/2024 02:24:32 PM

// Design Name:

// Module Name: xadc averager

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

```

```

module xadc averager #(

parameter int power = 8, // 2^8 = 256 samples

parameter int N = 8

// Bit width of input data

) (

input logic clk,

input logic reset,

input logic EN,

input logic [N-1:0] Din,

output logic [N-1:0] Q

);

// Declare register array and sum with proper widths

logic [N-1:0] REG ARRAY [2**power:1];

logic [power+N-1:0] sum; // Wide enough to hold full sum

// Average by taking upper bits of sum

assign Q = sum[power+N-1:power];

always ff @(posedge clk) begin

if (reset) begin

sum <= '0;

for (int j = 1; j \le 2^{**} power; j++) begin

REG_ARRAY[j] <= '0;

end

end

else if (EN) begin

// Update sum and shift register

sum <= sum + Din - REG_ARRAY[2**power];</pre>

for (int j = 2^{**}power; j > 1; j--) begin

REG ARRAY[i] <= REG ARRAY[i-1];

end

REG ARRAY[1] <= Din;

end

end

endmodule

module menu_FSM (

input logic

clk,

input logic

rst,

input logic

first_select,

input logic

second select,

input logic

third_select,

```

```

input logic

fourth_select,

down button select,

input logic

input logic [15:0] scaled adc data,

input logic [15:0] ave_xadc,

input logic [15:0] xadc raw,

input logic [7:0] pwm raw,

input logic [11:0] reg switches in,

input logic [7:0] r2r raw,

input logic [11:0] pwm avg,

input logic [15:0] pwm scaled,

input logic [11:0] r2r avg,

input logic [15:0] r2r scaled,

input logic [7:0] pwm_successive_raw,

input logic [7:0] r2r successive raw in,

output logic [15:0] mux_out,

output logic [3:0] decimal point

);

// State enumeration for all possible combinations

typedef enum logic [4:0] {

STATE_0000 = 5'd0, // reg_switches

STATE 0010 = 5'd1, // in1

STATE 0011 = 5'd2, // in2

STATE_0100 = 5'd3, // in7

STATE 0101 = 5'd4, // analog pwm avg

STATE 0110 = 5'd5, // in0

STATE_0111 = 5'd6, // analog_pwm

STATE 1000 = 5'd7, // pwm successive

STATE_1001 = 5'd8, // r2r_successive_raw

STATE 1010 = 5'd9, // in7

STATE 1011 = 5'd10, // analog r2r avg

STATE_1100 = 5'd11, // analog_r2r_raw

STATE 1101 = 5'd12, // analog r2r avg

STATE_1110 = 5'd13, // analog_pwm_avg

STATE 1111 = 5'd14 // in9

} state_t;

state_t current_state, next_state;

logic [3:0] select_inputs;

// Zero-extend all the smaller inputs

logic [15:0] analog_pwm;

logic [15:0] reg switches;

logic [15:0] analog_r2r_raw;

```

```

logic [15:0] analog_pwm_avg;

logic [15:0] analog r2r avg;

logic [15:0] pwm successive;

logic [15:0] r2r_successive_raw;

// Input processing

assign select_inputs = {fourth_select, third_select, second_select, first_select};

// Signal extensions

assign pwm_successive = {{8{1'b0}}, pwm_successive_raw};

assign analog_pwm = {{8{1'b0}}}, pwm_raw};

assign analog pwm_avg = {{4{1'b0}}}, pwm_avg};

assign reg_switches = {{4{1'b0}}}, reg_switches_in};

assign analog_r2r_avg = \{\{4\{1'b0\}\}\}, r2r_avg\};

assign analog_r2r_raw = {{8{1'b0}}}, r2r_raw};

assign r2r_successive_raw = {{8{1'b0}}}, r2r_successive_raw_in};

// State register

always_ff @(posedge clk) begin

if (rst)

current_state <= STATE_0000;

else

current state <= next state;

end

// Next state logic based on select inputs

always_comb begin

// Default: maintain current state

next_state = current_state;

// State transitions based on select inputs

case (select_inputs)

4'b0000: next state = STATE 0000;

4'b0010: next state = STATE 0010;

4'b0011: next state = STATE 0011;

4'b0100: next state = STATE 0100;

4'b0101: next state = STATE 0101;

4'b0110: next state = STATE 0110;

4'b0111: next state = STATE 0111;

4'b1000: next state = STATE 1000;

4'b1001: next state = STATE 1001;

4'b1010: next_state = STATE_1010;